This is a blog documenting various electronic projects that use microcontrollers. Comments, questions, and new ideas/projects are always welcomed.

Sunday, October 12, 2014

Nice Git Tutorial

Just a well done Git Tutorial for any newbies. http://git-scm.com/docs/gittutorial

Thursday, July 24, 2014

Tuesday, July 8, 2014

Coin BLE Firmware Updated

I updated the Coin BLE Firmware to work with the latest BLE SW Update Tool (1.2.2-100). See repository here on GitHub

Sunday, July 6, 2014

Simple Coin BLE Android App Now Available

The original Coin dev kit software only included an iOS app to test with the kit. I hacked together a bare-bones version for Android as well. The repo is live here on GitHub.

Friday, June 13, 2014

Cadence Allegro PCB Editor and Layout Tips

- When trying to save board real-estate, do not

necessarily get the smallest part/footprint available. Try to stick

with >=0.5mm pitch (0.3mm pitch is usually specific to cell phone

applications and usually requires separate fabrication line for assembly)

- Check any connectors to make sure orientation is

correct

- For LVDS connectors, try to get connectors that have

+/- side by side rather than vertically matched so you can length match

easier

- Try to keep LVDS and TTL signals on separate layers

- Check for availability and MOQ of parts once you have a system design (BEFORE layout). Make sure that parts are readily available and preferably at a low MOQ.

- Get parts that are easily interchangeable (i.e.

have popular footprints!!). This makes it easy to swap parts later in

the design process when you do not want to rebuild a board!

- Get a board stack-up from the board house,

giving them the impedance controls you need (for differential signals

mainly). Typical values are 100 Ohms for differential and 60-70 Ohms for

single ended traces. They will then provide you with a stack-up that will

tell you board thickness and trace widths and spacing information, all of

which you can input into your constraints before actually starting the

board layout

- Allegro PCB Editor: Help>>Documentation

- YouTube Cadence Tutorial Channel

- Reference Designer Tutorial for Allegro PCB Editor

- In Design Entry CIS, export Netlist: Click on .dsn file

in the File tree tab, then Tools>>Create Netlist

- Allegro PCB: File>>Import>>Netlist (make

sure location is same as where exported from Design Entry CIS)

- Place parts: Manually Place>>Components

by Refdes>>place parts

- Set which classes you want to view by clicking on the

Color192 button, can view active class in the Options menu in General Mode

- Etch: this

is where layers are accessed. For a 4 layer board it would be TOP, GND,

PWR, BOTTOM etch layers

- Board Geometry: under

this class lies the important subclass, Outline, which defines the boarder

of the board

- Package Keepin: class

that includes shapes that define where all packages must be inside or a

DRC error is thrown

- Route Keepin: class

that includes shapes that define where all traces/vias must be inside or a

DRC error is thrown

- Create shape (rectangle, polygon, circle, etc.) on the

desired layer

- Edit>>ZCopy

- In Options panel, select layer to copy to, set offset

(0 for exact copy)

- Click on shape>>Right Click>>Done

- Recommended to start with a previously made board as it

has a good format for manufacturing notes, design rules used before, etc.

- Create a layout folder under your

project folder, create new .brd file here or copy someone else's board

into this directory

- Tip: leave all footprints and padstacks directly in

this folder, clean up into specific .zip files at end of board

development, this will save you a lot of trouble down the road as you

won't have to change/check the Path all the time

- If using an old design, delete all previous board using

the Delete button and selecting the All On button in the Find menu

- Create board outline shape (Class: Package Geometry

Subclass: Outline)

- Create package keepin shape (Class: Package Keepin)

- Create route keepin shape (Class: Route Keepin)

- Import netlist (see above instructions)

- Place parts

- Connect traces, following all design rules

- Tools>>Padstack>>Modify Design Padstack

- Changes or saved padstacks will not show up in current

.brd or .dra file immediately. To update an existing padstack: Modify

Design Padstack>>make your changes on both Instance and Definition

Edit options>>Save As (save in your layout

folder)>>Tools>>Padstack>>Refresh...>>Refresh

- Go into Placementedit mode ( RC>>Application

Mode >> Placement Edit)

- Highlight the components/vias/etc you want to align

(make sure you can select the right part in the Find panel)

- RC>>Align Components

- In the options panel, specify orientation and set the

spacing

- For a hole (like a fixing/fiducial hole): Place>>Manually>>Drop

down from Components by Refdes to Mechanical Symbols

- If it is not already there, make a new one: File>>New>>Mechanical

Symbol

- Add Connect>>Right Click>>Multi-Trace Route

- First you must designate signals as differential pair

under Constraint Manager (open up Constraint Manager-CM Button)

- Click on Electrical Tab>>Net>>Total

Etch Length (or any of the categories), then

Objects>>Create...>>Differential Pair>>enter Diff Pair

Name and select pair>>Create

- You can also do auto setup from the Differential Pair

menu: Auto Setup>>(if smart and named diff pair signals with

+ and - in them)>>type '+' in + Filter and '-' in the -

Filter>>Create

- Now signals will be routed according to the Diff Pair

DRC rules: Adjust those in Constraint Manager (CM)

- Typical Constraints for Diff Pairs:

- Length matched under Total Etch Length within 5 mils

- Min line spacing: 4 mils

- Primary Gap: 4.92 mils

- Neck Width: 4 mils,

- Tolerance +/-: .920

- Whenever you are routing, moving, tuning a diff pair,

you can Right Click>>Single Trace Mode to only

perform actions on one of the traces

- It is a good idea to group signals together for length

matching and easier readability; you do this by adding signals to classes

- In the CM, click on the Net folder>>Any

category>>highlight signals you want to group>>Right

Click>>Create...>>Net Class...>>name the class>>OK

- A CSet is used to set a signal/class to a specific set

of design rules i.e. for differential pairs

- Click the drop down menu on any signal under the

"ReferencedC Set" and select desired C Set

- Typical set names/categories are: DEFAULT, DIFFPAIR,

PWR

- Electrical Tab>>Electrical Constraint Set

folder>>Select Desired

Category>>Objects>>Create...>>Electrical

CSet...>>then set your constraints for that set

- Set your length constraints in CM (tip: route the trace

that looks like it will be the longest and use that length as your average

between max/min in length constraint, set your min/max based on this

number in CM, route the others, the meter at the bottom will tell you

using green or red whether or not your trace is within the min/max set)

- Use the Delay Tuning button to

lengthen a trace that is shorter than desired length

- Use the Slide button to adjust a trace

to shorten it (take a more direct path or make that trace your reference

trace for the min/max length): avoid using Trombone or Accordion tuning

styles on differential pairs

- Setup>>Change drawing origin

- Click on whatever shape/symbol/etc you are placing

moving, click down in the command line window, place at proper coordinates

for exact placing/sizing using "x y " relative to the

origin (0,0). You can also move relative to one axis using "ix "

or "iy "

- If what you are editing is a shape, you must first

decompose this into lines: Shape>>Decompose Shape, in

the Options menu select layer to copy to as the same layer the shape

currently is and check the Delete shape after decompose box,

it is now made up of lines

- Manufacturing>>Drafting>>Chamfer/Filet, input parameters and click on the two corner lines

you want to chamfer/filet

- Route>>Create Fanout

- Use to automatically route a bunch of fanouts the same

time, especially useful for BGA's

- Can copy fanout once complete: YouTube Tutorial

- Locate the files and copy into layout

directory where board (.brd) is located

- File>>Import>>IPF, select file and before placing it, right

click and use the Scale option to properly size, change

to proper layer

- Pick and place tool needs a reference point, so place

at least 2 of these on the top layer of the board...and

add as mechanical symbol (see above instructions on How to

manually add a PAD/VIA)

- Sometimes it helps to delete all .PAD, .PSM, .BRD, and

.DRA files out of the folder in order to clean up layout folder. Several

times this has fixed my import issues.

- Another common error is missing the padstack from a

.DRA file that was added in (i.e. from someone else's design, etc.). Even

though the padstack is internally attached to the .DRA file, it also needs

to be present locally in your layout folder. To get the padstack, open up

the .DRA file. Click Tools>>Padstack>>Modify design

padstack. For each of the pads in the Options window, click Edit and

in the Padstack Editor click File>>Save As.., saving it

in your layout file. As described in the padstack edit section above, edit

both the Definition and Instance and refresh the padstack. Then save the .DRA

file. You now have all of the proper .DRA, .PSM, and .PAD files for that

footprint.

- Place>Update Symbols, and check on the desired symbols

- Setup>Cross Section

- For manufacturing you need to provide the following

files:

- Gerbers

- Drill

- Placement

- IPC

- Stackup

- Any special instructions

- To generate Gerber & NC Drill files from OrCAD (Cadence

Allegro) PCB Editor, Open the native file (.BRD) in OrCAD PCB

Editor.

- Gerber Files: From the Editors window, go to

Manufacture > Artwork; on the Artwork Control Form, click on the

General Parameters tab to make active and then confirm the following

settings:

- Device Type ~ Gerber RS274X

- Film Size Limits ~ 14 x 16

- Leave remaining default settings to keep outputs

consistent. Now, click on the Film Control tab and choose Select all from

the bottom of the Available Films section and then Create Artwork. Choose

OK to close this window. The artwork (Gerber files) should now reside in

the originating folder (where your .brd file is located).

- NC Drill File : From the Editors window, go to

Manufacture > NC > NC Drill. The NC Drill dialog box will open.

Confirm that the root file name is present (board name.drl) and choose 'Auto

Tool Select'. Leave remaining default selections. Click on the Drill

button to generate the NC Drill file. The NC Drill file should now reside

in the originating folder.

- IPC files: Got to File > Export > IPC 356... >

select IPC Version IPC-D-356A > Export

- Placement file: File > Export > Placement >

Leave standard settings > Export

- Also include any special fab instructions

- Click on Add Connect button

- Click on pad/pin/trace to route from and route trace,

then right click >> Done

- Click on Add Connect button again

- Click on same pad/pin/trace to route from before

- In the Options panel, uncheck the

"Replace etch" box

- Rout the second trace

- Go to board stackup: Setup>>Cross Section

- Check "Show Single Impedance" and "Show

Diff Impedance" boxes

- If you have a layer with Diff Pairs on it, select Edge

as Coupling Type

- Set the Impedance for single and differential- Allegro

will then adjust the spacing and trace widths accordingly

- Click "Report" to send to board house, they will adjust it to their equipment etc and provide you with a slightly different stackup

- Pads are usually much larger than the trace widths that

run to/from them. Because of this, they will have an increased

capacitance, lowering the impedance through the pad possibly creating

reflections, degrading the signal (especially at higher speeds). In order

to maintain impedance, cutouts must be made underneath the pads to the

point where the impedance matches that of the trace.

- See David Lieby's notes on cutouts in the reference

sections of Signal Integrity and LVDS for calculations, etc.

READ FOLLOWING DOCUMENTS ON LVDS LAYOUT. These

are very important and well written.

- Altera Board Design

Guidelines for LVDS Systems

- T.I. Design Notes 2000: LVDS (Older)

- National Semiconductor 2004 LVDS Owner's Manual

- Fairchild Semiconductor 2005 LVDS Fundamentals

- See Signal Integrity section below for more tips

- Create a project folder, within this folder, create a

"Netlist", "Components", and "Library"

folder

- File>>New>>Project

- Under "Location", Browse to the project

folder you just created

- Type in project name and select "Schematic"

radio button, click OK

- In file hierarchy tab (.obj tab), RC on

"Library" folder>>Add File

- RC on your new library, click "Save As" and

save under your "Library" folder you created at the beginning

- As you add parts (mainly IC's), place the datasheets in

the "Components" folder

- RC on your library in .obj tab, click "New

Part"

- Type in the name (usually a Manufacturing PN)

- Select part reference prefix: C for capacitors, R for

Resistors, J for headers/connectors, and U for ICs

- Press OK, change shape/look as you like (usually a

rectangle is standard)

- Place pins (get from datasheet), set type to Power for

GND, VCC, etc and select "Pin Visible" as this will allow you to

have several pins with same name i.e. GND, VCC, AGND, AVCC

- Place inputs on left hand side, outputs on right hand

side, group grounds and power

- If there is a DAP or large GND pad, add it as an

additional pin for layout

- Assign footprint to part under part properties (name

needs to match name of .dra file in the same folder as the layout)

- Click on .dsn file in .obj tab so that it is

highlighted

- Tools>>Create Netlist ...

- Check the Create PCB Editor Netlist

- Specifiy your Netlist Files Directory as the

"Netlist" folder you created at setup (this will be the same

place you will import your netlist in Allegro during layout)

- Click OK

- "I have two Allegro PCB Editor board files. I need

to merge them and make a single board. How can I do this?"

- If the two schematic files are also available, follow

the steps below:

- Assign unique refdes in the schematics and board files

- Merge the two schematics

- Generate the Allegro netlist and read that netlist

into the larger board

- Open the smaller board

- Select File > Export > Sub-drawing

- Check the "Preserve Refdes" button from the

"Options" tab

- Select the whole board and pick an origin point

- Save the subdrawing as file type .clp

- Open the larger board in PCB Editor

- Select File > Import > Sub-drawing to import the

above .clp file and place it on the board

- If only the board files are available, follow the steps

below:

- Open one board and select Tools > Create Module

- Window around the entire board

- Select an origin

- Save the module as file type .mdd.

- Open the second board

- Select Place > Manually

- Select "Module Definition" from the drop

down list in the Placement List tab

- Select the module. If you are selecting the module

from a modulepath, then you need to check in Library from Place >

Manually> Advanced Settings

- Enter any letter in the Module Instance name, say d

- The module gets placed on the board, with refdes named

as d_D1, nets as d_N005, etc. You can rename both the refdes and nets.

- Analyzing your design to ensure proper decoupling

capacitors

- One such Power Distribution Network analysis tool

available to help calculate the proper number/type of bypass capacitors

for your board design. It is located here

- The tool is well documented (User Guide at same

location)

- Use Hyperlinx to simulate your high speed design after the board is complete

- Signal Integrity

Effects of Vias, Stubs, and Minimizing their Visibility

- Altera: Impact of I/O Settings on Signal Integrity in

Stratix III Devices

- Controlled Impedance Guide

- PCIe High Speed Layout Guide

Labels:

allegro pcb editor,

board design,

cad,

cadence,

design entry cis,

layout,

pcb design,

signal integrity

Thursday, June 12, 2014

CycleAT - New Project Intro Video

Check out the Teaser video for our new HW project.

Web: www.cycleat.com

Facebook: www.facebook.com/cycleat

Web: www.cycleat.com

Facebook: www.facebook.com/cycleat

Tuesday, April 29, 2014

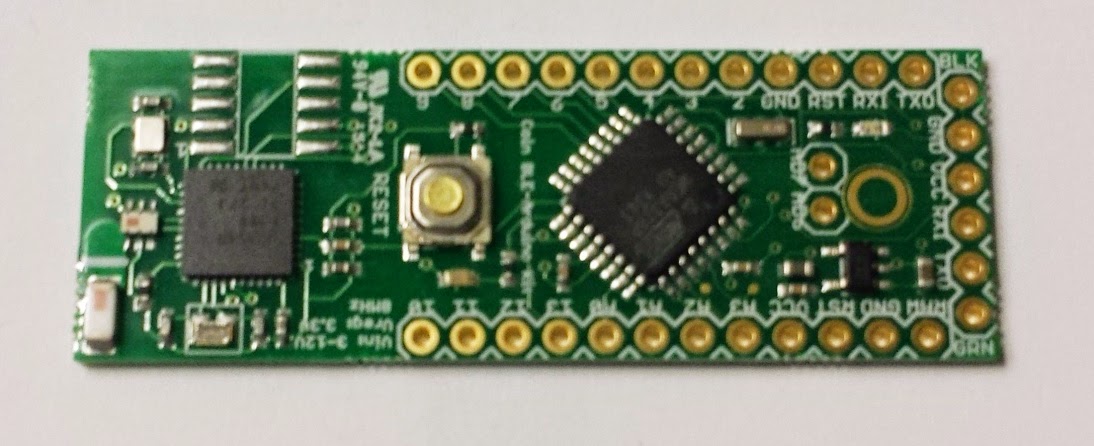

Setting up the Coin BLE Dev Kit

The following instructions are for setting up a brand new Coin BLE Dev Board for easy programming with the Arduino IDE and Bluetooth integration. Even though the original boards sold out and Coin did not plan on doing another manufacturing run, many people were still interested in getting their hands on these boards. Because of this, our team took over the second manufacturing run so that everyone who wants the board can get one.

To purchase your own Coin BLE Dev Board (NO LONGER AVAILABLE), visit http://coindev2.myshopify.com/

The boards come assembled fresh from the factory, so this post documents the steps that must be followed to get your board programming ready.

The original Coin BLE Wiki can be found at https://github.com/CoinApps/arduino-ble-dev-kit/wiki

To Program the BLE module:

- For default BLE behavior (send 1 byte at a time from the Arduino via Bluetooth) or if you do not want to write any custom code for the BLE module, program the out1-19-NOV-2013.hex file provided on the Coin Wiki (Git Hub Link to code)

- Follow the instructions to program the BLE module here: Coin Wiki for BLE Software Instructions

To Program the Bootloader on the Arduino

2 Methods:

- Using the Atmel mkII AVRISP Programmer

- Using another Arduino and the Arduino IDE

Method 1: Atmel mkII AVRISP Programmer

Requirements:

- 6 pin 0.1" male-to-male header

- Jumper wires

- Coin BLE Dev Board

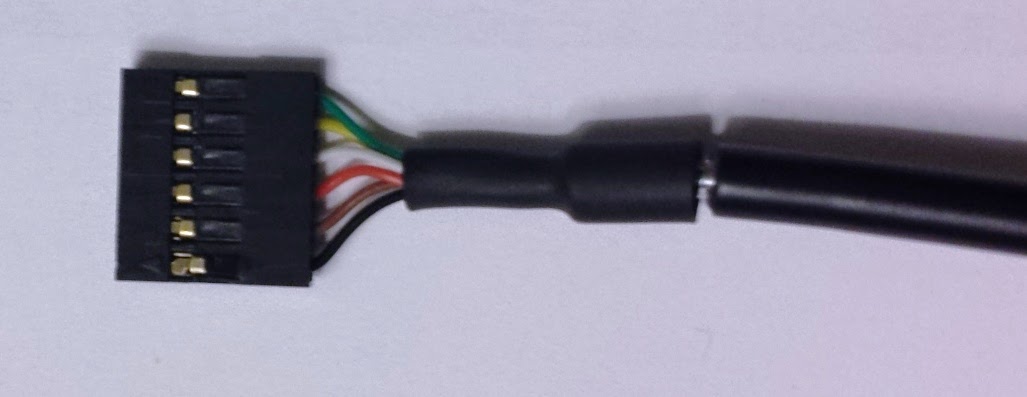

- FTDI Programming Cable

- Atmel mkII AVRISP Programmer (~$37.00)

- Atmel Studio 6 or Atmel Studio 6 Programmer Standalone (free software, download link here)

- Jumper wires

Instructions:

1) Place 6 pin header into the FTDI cable

2) Wire the following pins up to the mkII programmer (no need to solder them in, just bend to ensure pin contact)

|

| ***Taken from http://www.avrfreaks.net/index.php?name=PNphpBB2&file=printview&t=81538 *** |

3) Place FTDI cable into dev board for powering the board (the red light will be on). Make sure you orient the FTDI cable correctly when you connect it (the board says GRN on the side that corresponds to the green wire on the FTDI cable)

4) Open up Atmel Studio 6: Tools >> Device Programming

5) When the programming window pops up, set up the following properties

- Tool: Select AVRISP mkII

- Device: ATA6614Q

6) Click Apply

7) IMPORTANT: Under the Interface Settings tab, set the ISP Clock to 125kHz (for the first time this must be done since the fuse settings haven't been set yet)

8) Under the Memories tab, browse for the ATmegaBOOT_168_atmega328_pro_8MHz.hex bootloader (under most normal Windows installs, this will be located under C:\Program Files (x86)\Arduino\hardware\arduino\bootloaders\atmega\)

9) Click Program

10) Upon success, go the the Fuses tab and set the fuses to the following:

- EXTENDED: 0xFD

- HIGH: 0XDA

- LOW: 0XFF

11) Click Program

12) Now verify that the bootloader was properly loaded by opening up the Arduino IDE and loading the "Blink.ino" file onto the dev board using the FTDI cable only as the following describes:

- Select the proper serial port where your FTDI programming cable is plugged into

- Under Board, select Arduino Pro or Pro Mini (3.3V, 8MHz) w/ATmega328

Method 2: Use another Arduino as a AVRISP programmer

The second method is to use another Arduino to program the bootloader. This can be done with the setup seen below, except for replacing the top Arduino with the dev kit board. Modified from http://arduino.cc/en/Tutorial/ArduinoToBreadboard.

If you have a new ATmega328 (or ATmega168), you'll need to burn the bootloader onto it. You can do this using an Arduino board as an in-system program (ISP). If the microcontroller already has the bootloader on it (e.g. because you took it out of an Arduino board or ordered an already-bootloadedATmega), you can skip this section.

To burn the bootloader, follow these steps:

- Upload the ArduinoISP sketch onto your Arduino board that you will be burning the bootloader from (You'll need to select the board and serial port from the Tools menu that correspond to your board.) This can be found in the Arduino IDE at File >> Examples >> ArduinoISP. Upload this sketch to the device.

- Wire up the Arduino board and microcontroller as shown below. The 4 yellow wires in the image from the programmer Arduino should instead be contacted with the following pins on the dev board (once again, just make sure you have contacts on the pins using the jumper wires rather than soldering them completely in if you want to save some time):

- PIN 13 on programmer Arduino <--> PIN 13 on dev board

- PIN 12 on programmer Arduino <--> PIN 12 on dev board

- PIN 11 on programmer Arduino <--> PIN 11 on dev board

- PIN 10 on programmer Arduino <--> RST on dev board

- Select "Arduino Pro or Pro Mini (3.3V, 8MHz)w/ATmega328" from the Tools > Board menu (see below ):

- PIN 13 on programmer Arduino <--> PIN 13 on dev board

- PIN 12 on programmer Arduino <--> PIN 12 on dev board

- PIN 11 on programmer Arduino <--> PIN 11 on dev board

- PIN 10 on programmer Arduino <--> RST on dev board

- Run Tools > Burn Bootloader > w/ Arduino as ISP.

- Finally, select Burn Bootloader from the Tools menu to burn the bootloader onto the board.

Now verify that the bootloader was properly loaded by opening up the Arduino IDE and loading the "Blink.ino" file onto the dev board using the FTDI cable only.

Now verify that the bootloader was properly loaded by opening up the Arduino IDE and loading the "Blink.ino" file onto the dev board using the FTDI cable only.

You should only need to burn the bootloader once. After you've done so, you can remove the jumper wires connected to pins 10, 11, 12, and 13 of the Arduino board.

- Connect the FTDI programmer to the dev board (see above steps on how to do this)

- Select the proper serial port where your FTDI programming cable is plugged into

- IMPORTANT: Under Board, select Arduino Pro or Pro Mini (3.3V, 8MHz) w/ATmega328

- Click Upload Sketch button in the IDE

More info on using Arduino as AVRISP bootload burner:

- The Arduino setup page for this can be found here: http://arduino.cc/en/Tutorial/ArduinoToBreadboard

- Another reference: http://www.instructables.com/id/Turn-Your-Arduino-Into-an-ISP/

Program the Arduino with the Example Programs from the Coin Wiki

- Download the example code seen here from the Wiki

- Load the code onto the Arduino in the same manner as you did the "Blink.ino" above

Labels:

Arduino,

BLE,

Bluetooth,

Coin BLE Dev Kit,

Low Power,

Microcontroller

Subscribe to:

Comments (Atom)